Konstrukcja magistral I/O reprezentuje arterie komputerowe i znacząco determinuje, jak dużo i jak szybko dane mogą być wymieniane pomiędzy poszczególnymi komponentami wymienionymi powyżej. Najwyższą kategorię wiodą komponenty stosowane w dziedzinie obliczeń o wysokiej wydajności (HPC). Od połowy 2020 r. wśród współczesnych przedstawicieli HPC są Nvidia Tesla i DGX, Radeon Instinct oraz akceleratory oparte na procesorach graficznych Intel Xeon Phi (porównania produktów patrz [1,2]).

Zrozumienie NUMA

Non-Uniform Memory Access (NUMA) opisuje architekturę pamięci współdzielonej stosowaną we współczesnych systemach wieloprocesorowych. NUMA to system obliczeniowy składający się z kilku pojedynczych węzłów w taki sposób, że zagregowana pamięć jest współdzielona pomiędzy wszystkie węzły: „każdy procesor ma przypisaną własną pamięć lokalną i może uzyskać dostęp do pamięci z innych procesorów w systemie” [12,7].

NUMA to sprytny system służący do łączenia wielu jednostek centralnych (CPU) z dowolną ilością pamięci komputera dostępnej w komputerze. Pojedyncze węzły NUMA są połączone za pośrednictwem skalowalnej sieci (magistrali we/wy), dzięki czemu procesor może systematycznie uzyskiwać dostęp do pamięci powiązanej z innymi węzłami NUMA.

Pamięć lokalna to pamięć używana przez procesor w określonym węźle NUMAA. Pamięć obca lub zdalna to pamięć, którą procesor pobiera z innego węzła NUMA. Termin NUMA ratio opisuje stosunek kosztu dostępu do pamięci obcej do kosztu dostępu do pamięci lokalnej. Im wyższy współczynnik, tym wyższy koszt, a co za tym idzie, dłużej trwa dostęp do pamięci.

Jednak trwa to dłużej niż wtedy, gdy ten procesor uzyskuje dostęp do własnej pamięci lokalnej. Dostęp do pamięci lokalnej jest główną zaletą, ponieważ łączy niskie opóźnienia z wysoką przepustowością. W przeciwieństwie do tego, dostęp do pamięci należącej do dowolnego innego procesora ma większe opóźnienia i niższą przepustowość.

Patrząc wstecz: ewolucja multiprocesorów z pamięcią współdzieloną

Frank Dennemann [8] stwierdza, że nowoczesne architektury systemów nie pozwalają na prawdziwie jednolitego dostępu do pamięci (UMA), mimo że systemy te są specjalnie zaprojektowane do tego celu. Mówiąc najprościej, ideą obliczeń równoległych było posiadanie grupy procesorów, które współpracują przy obliczaniu danego zadania, przyspieszając w ten sposób klasyczne obliczenia sekwencyjne.

Jak wyjaśnił Frank Dennemann [8], na początku lat 70. „zapotrzebowanie na systemy, które mogłyby obsługiwać wiele równoczesnych operacji użytkowników i nadmierne generowanie danych, stało się głównym nurtem” wraz z wprowadzeniem relacyjnych systemów baz danych. „Pomimo imponującej wydajności procesorów jednoprocesorowych, systemy wieloprocesorowe były lepiej przygotowane do obsługi tego obciążenia. Aby zapewnić opłacalny system, przedmiotem badań stała się przestrzeń adresowa pamięci współdzielonej. Na początku zalecano systemy wykorzystujące przełącznik krzyżowy, jednak złożoność projektu skalowała się wraz ze wzrostem liczby procesorów, co czyniło system oparty na magistrali bardziej atrakcyjnym. Procesory w systemie magistrali [mogą] uzyskać dostęp do całej przestrzeni pamięci poprzez wysyłanie żądań do magistrali, bardzo opłacalny sposób na optymalne wykorzystanie dostępnej pamięci.”

Jednak systemy komputerowe oparte na magistrali mają wąskie gardło – ograniczona przepustowość, która prowadzi do problemów ze skalowalnością. Im więcej procesorów zostanie dodanych do systemu, tym mniejsza dostępna przepustowość na węzeł. Co więcej, im więcej procesorów zostanie dodanych, tym dłuższa magistrala i tym większe opóźnienie.

Większość procesorów została skonstruowana w płaszczyźnie dwuwymiarowej. Procesory musiały również mieć dodane zintegrowane kontrolery pamięci. Proste rozwiązanie polegające na posiadaniu czterech magistral pamięci (góra, dół, lewo, prawo) dla każdego rdzenia procesora pozwalało na pełną dostępną przepustowość, ale to tylko do tej pory. Procesory z czterema rdzeniami przez długi czas pozostawały w stagnacji. Dodanie śladów powyżej i poniżej umożliwiło bezpośrednie połączenie autobusów z procesorami po przekątnej, gdy układy stały się 3D. Kolejnym logicznym krokiem było umieszczenie czterordzeniowego procesora na karcie, która następnie została podłączona do magistrali.

Obecnie każdy procesor zawiera wiele rdzeni ze współdzieloną pamięcią podręczną na chipie i pamięcią poza chipem oraz ma zmienne koszty dostępu do pamięci w różnych częściach pamięci w serwerze.

Poprawa wydajności dostępu do danych jest jednym z głównych celów współczesnego projektowania procesorów. Każdy rdzeń procesora był wyposażony w małą pamięć podręczną pierwszego poziomu (32 KB) i większą (256 KB) pamięć podręczną drugiego poziomu. Poszczególne rdzenie będą później współdzielić pamięć podręczną poziomu 3 o wielkości kilku MB, której rozmiar z biegiem czasu znacznie się zwiększył.

Aby uniknąć chybień w pamięci podręcznej - żądania danych, których nie ma w pamięci podręcznej - dużo czasu poświęca się na znalezienie odpowiedniej liczby pamięci podręcznych procesora, struktur pamięci podręcznej i odpowiednich algorytmów. Zobacz [8], aby uzyskać bardziej szczegółowe wyjaśnienie protokołu buforowania snoop [4] i spójności pamięci podręcznej [3,5], a także pomysły projektowe stojące za NUMA.

Wsparcie oprogramowania dla NUMA

Istnieją dwa sposoby optymalizacji oprogramowania, które mogą poprawić wydajność systemu obsługującego architekturę NUMA - koligacja procesora i rozmieszczenie danych data. Jak wyjaśniono w [19], „powinowactwo procesora […] umożliwia wiązanie i usuwanie powiązania procesu lub wątku z pojedynczym procesorem lub szeregiem procesorów, dzięki czemu proces lub wątek będzie wykonywany tylko na wyznaczonym procesorze lub procesorach, a nie niż jakikolwiek procesor.„Termin „umieszczanie danych” odnosi się do modyfikacji oprogramowania, w których kod i dane są przechowywane jak najbliżej pamięci.

Różne systemy operacyjne związane z UNIX i UNIX obsługują NUMA w następujący sposób (poniższa lista pochodzi z [14]):

- Obsługa Silicon Graphics IRIX dla architektury ccNUMA powyżej 1240 procesorów z serią serwerów Origin.

- W systemach Microsoft Windows 7 i Windows Server 2008 R2 dodano obsługę architektury NUMA na 64 rdzeniach logicznych.

- Wersja 2.5 jądra Linux zawierało już podstawową obsługę NUMA, która została dodatkowo ulepszona w kolejnych wydaniach jądra. Wersja 3.8 jądra Linux przyniosło nową podstawę NUMA, która pozwoliła na rozwój wydajniejszych polityk NUMA w późniejszych wydaniach jądra [13]. Wersja 3.13 jądra Linuksa wprowadziło wiele zasad, które mają na celu umieszczenie procesu w pobliżu jego pamięci, wraz z obsługą przypadków, takich jak udostępnianie stron pamięci między procesami lub użycie przezroczystych dużych stron; nowe ustawienia sterowania systemem umożliwiają włączanie i wyłączanie równoważenia pamięci NUMA, a także konfigurację różnych parametrów równoważenia pamięci NUMA [15].

- Zarówno Oracle, jak i OpenSolaris modelują architekturę NUMA z wprowadzeniem grup logicznych.

- FreeBSD dodało początkową konfigurację koligacji i polityki NUMA w wersji 11.0.

W książce „Computer Science and Technology, Proceedings of the International Conference (CST2016)” Ning Cai sugeruje, że badania nad architekturą NUMA koncentrowały się głównie na wysokiej klasy środowisku obliczeniowym i zaproponowano partycjonowanie Radix (NaRP) uwzględniające technologię NUMA, które optymalizuje wydajność współdzielonych pamięci podręcznych w węzłach NUMA w celu przyspieszenia aplikacji Business Intelligence. W związku z tym NUMA reprezentuje pośrednią płaszczyznę między systemami pamięci współdzielonej (SMP) z kilkoma procesorami [6].

NUMA i Linux

Jak wspomniano powyżej, jądro Linux obsługuje NUMA od wersji 2.5. Zarówno Debian GNU/Linux, jak i Ubuntu oferują obsługę NUMA do optymalizacji procesów za pomocą dwóch pakietów oprogramowania numactl [16] i numad [17]. Za pomocą polecenia numactl możesz wyświetlić spis dostępnych węzłów NUMA w Twoim systemie [18]:

# numactl -- sprzętdostępne: 2 węzły (0-1)

węzeł 0 procesor: 0 1 2 3 4 5 6 7 16 17 18 19 20 21 22 23

rozmiar węzła 0: 8157 MB

węzeł 0 wolny: 88 MB

węzeł 1 procesor: 8 9 10 11 12 13 14 15 24 25 26 27 28 29 30 31

rozmiar węzła 1: 8191 MB

węzeł 1 wolny: 5176 MB

odległości węzłów:

węzeł 0 1

0:10 20

1:20 10

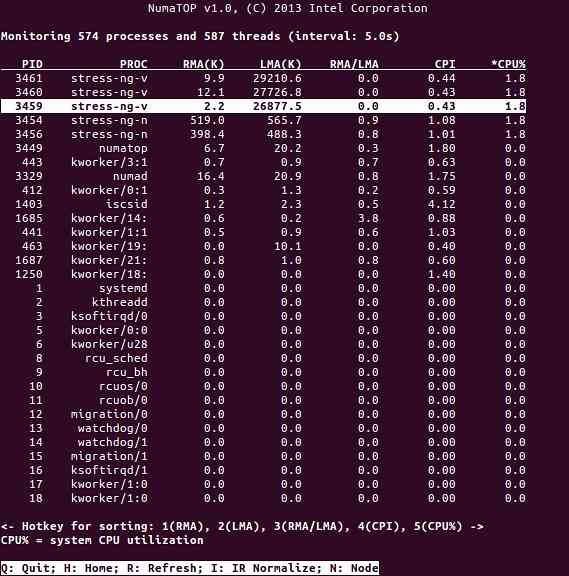

NumaTop to przydatne narzędzie opracowane przez firmę Intel do monitorowania lokalizacji pamięci uruchomieniowej i analizy procesów w systemach NUMA [10,11]. Narzędzie może identyfikować potencjalne wąskie gardła wydajności związane z NUMA, a tym samym pomagać w ponownym zrównoważeniu alokacji pamięci/procesora, aby zmaksymalizować potencjał systemu NUMA. Zobacz [9], aby uzyskać bardziej szczegółowy opis.

Scenariusze użytkowania

Komputery obsługujące technologię NUMA umożliwiają wszystkim procesorom bezpośredni dostęp do całej pamięci — procesory widzą to jako pojedynczą, liniową przestrzeń adresową. Prowadzi to do bardziej efektywnego wykorzystania 64-bitowego schematu adresowania, co skutkuje szybszym przepływem danych, mniejszą replikacją danych i łatwiejszym programowaniem.

Systemy NUMA są dość atrakcyjne dla aplikacji serwerowych, takich jak data mining i systemy wspomagania decyzji. Co więcej, dzięki tej architekturze pisanie aplikacji do gier i oprogramowania o wysokiej wydajności staje się znacznie łatwiejsze easier.

Wniosek

Podsumowując, architektura NUMA zajmuje się skalowalnością, która jest jedną z jej głównych zalet. W procesorze NUMA jeden węzeł będzie miał większą przepustowość lub mniejsze opóźnienie, aby uzyskać dostęp do pamięci w tym samym węźle (np.sol., lokalny CPU żąda dostępu do pamięci w tym samym czasie, co dostęp zdalny; priorytet ma lokalny procesor). To znacznie poprawi przepustowość pamięci, jeśli dane zostaną zlokalizowane w określonych procesach (a tym samym procesorach). Wadą są wyższe koszty przenoszenia danych z jednego procesora na drugi. Dopóki taki przypadek nie zdarza się zbyt często, system NUMA przewyższa systemy o bardziej tradycyjnej architekturze.

Linki i referencje

- Porównaj NVIDIA Tesla i. Instynkt Radeona, https://www.itcentralstation.com/products/comparisons/nvidia-tesla_vs_radeon-instinct

- Porównaj NVIDIA DGX-1 z. Instynkt Radeona, https://www.itcentralstation.com/products/comparisons/nvidia-dgx-1_vs_radeon-instinct

- Spójność pamięci podręcznej, Wikipedia, https://en.Wikipedia.org/wiki/Cache_coherence

- Śledzenie autobusów, Wikipedia, https://en.Wikipedia.org/wiki/Bus_snooping

- Protokoły koherencji pamięci podręcznej w systemach wieloprocesorowych, Geeks for geeks, https://www.geeksforgeek.org/protokoły-spójności-cache-w-systemie-wieloprocesorowym/

- Informatyka i technologia - Proceedings of the International Conference (CST2016), Ning Cai (Ed.), World Scientific Publishing Co Pte Ltd, ISBN: 9789813146419

- Daniel P. Bovet i Marco Cesati: Understanding NUMA architecture in Understanding the Linux Kernel, wydanie 3, O'Reilly, https://www.oreilly.com/library/view/understanding-the-linux/0596005652/

- Frank Dennemann: Głębokie nurkowanie NUMA, część 1: Od UMA do NUMA, https://frankdenneman.nl/2016/07/07/numa-deep-dive-part-1-uma-numa/

- Colin Ian King: NumaTop: narzędzie do monitorowania systemu NUMA, http://smackerelofopinion.blogspot blog.com/2015/09/numatop-numa-system-monitoring-narzędzie.html

- Numatop, https://github.com/intel/numatop

- Pakiet numatop dla Debiana GNU/Linux, https://packages.debian.org/buster/numatop

- Jonathan Kehayias: Zrozumienie niejednolitego dostępu do pamięci/architektur (NUMA), https://www.sqskills.com/blogs/jonathan/understanding-non-uniform-memory-accessarchitectures-numa/

- Wiadomości o jądrze Linux dla jądra 3.8, https://kernelnewbies.org/Linux_3.8

- Niejednolity dostęp do pamięci (NUMA), Wikipedia, https://en.Wikipedia.org/wiki/Non-uniform_memory_access

- Dokumentacja zarządzania pamięcią w systemie Linux, NUMA, https://www.jądro.org/doc/html/latest/vm/numa.html

- Pakiet numactl dla Debiana GNU/Linux, https://packages.debian.org/sid/admin/numactl

- Numer pakietu dla Debiana GNU/Linux, https://packages.debian.org/buster/numad

- Jak sprawdzić, czy konfiguracja NUMA jest włączona, czy wyłączona??, https://www.dzienniczek geeków.com/centos-rhel-jak-znaleźć-jeśli-numa-configuration-is-enable-or-disable/

- Powinowactwo procesora, Wikipedia, https://en.Wikipedia.org/wiki/Processor_affinity

Dziękuję Ci

Autorzy dziękują Geroldowi Rupprechtowi za wsparcie w przygotowaniu tego artykułu.

O Autorach

Plaxedes Nehanda to wszechstronna, samodzielna i wszechstronna osoba, która nosi wiele kapeluszy, między innymi planistkę wydarzeń, wirtualną asystentkę, transkrypcję, a także zapaloną badaczkę z Johannesburga w RPA.

Książę K. Nehanda jest inżynierem ds. oprzyrządowania i kontroli (metrologii) w Paeflow Metering w Harare, Zimbabwe.

Frank Hofmann pracuje w drodze - najlepiej z Berlina (Niemcy), Genewy (Szwajcaria) i Kapsztadu (RPA) - jako programista, trener i autor magazynów takich jak Linux-User i Linux Magazine. Jest także współautorem książki o zarządzaniu pakietami Debiana (http://www.dpmb.organizacja).

Phenquestions

Phenquestions